Epson Research and Development Page 95

Vancouver Design Center

Hardware Functional Specification S1D13504

Issue Date: 01/01/30 X19A-A-002-18

bit 7 Vertical Non-Display Period Status

This is a read-only status bit. A “1” indicates that a vertical non-display period is occurring. A “0”

indicates that display output is in a vertical display period.

Note

When configured for a dual panel, this bit will toggle at twice the frame rate.

bits 5-0 Vertical Non-Display Period Bits [5:0]

These bits specify the vertical non-display period height in 1-line resolution.

Vertical non-display period height in number of lines = (ContentsOfThisRegister) + 1.

The maximum vertical non-display period height is 64 lines.

Note

This register must be programmed such that

REG[0Ah] ≥ 1 and (REG[0Ah] bits [5:0] + 1) ≥ (REG[0Bh] + 1) + (REG[0Ch] bits [2:0] + 1)

bits 5-0 VRTC/FPFRAME Start Position Bits [5:0]

For CRTs and TFTs, these bits specify the delay in lines from the start of the vertical non-display

period to the leading edge of the VRTC pulse and FPFRAME pulse respectively. For passive LCDs,

FPFRAME is automatically created and these bits have no effect.

VRTC/FPFRAME start position (lines) = VRTC/FPFRAME Start Position Bits [5:0] + 1.

The maximum VRTC start delay is 64 lines.

Note

This register must be programmed such that

(REG[0Ah] bits [5:0] + 1) ≥ (REG[0Bh] + 1) + (REG[0Ch] bits [2:0] + 1)

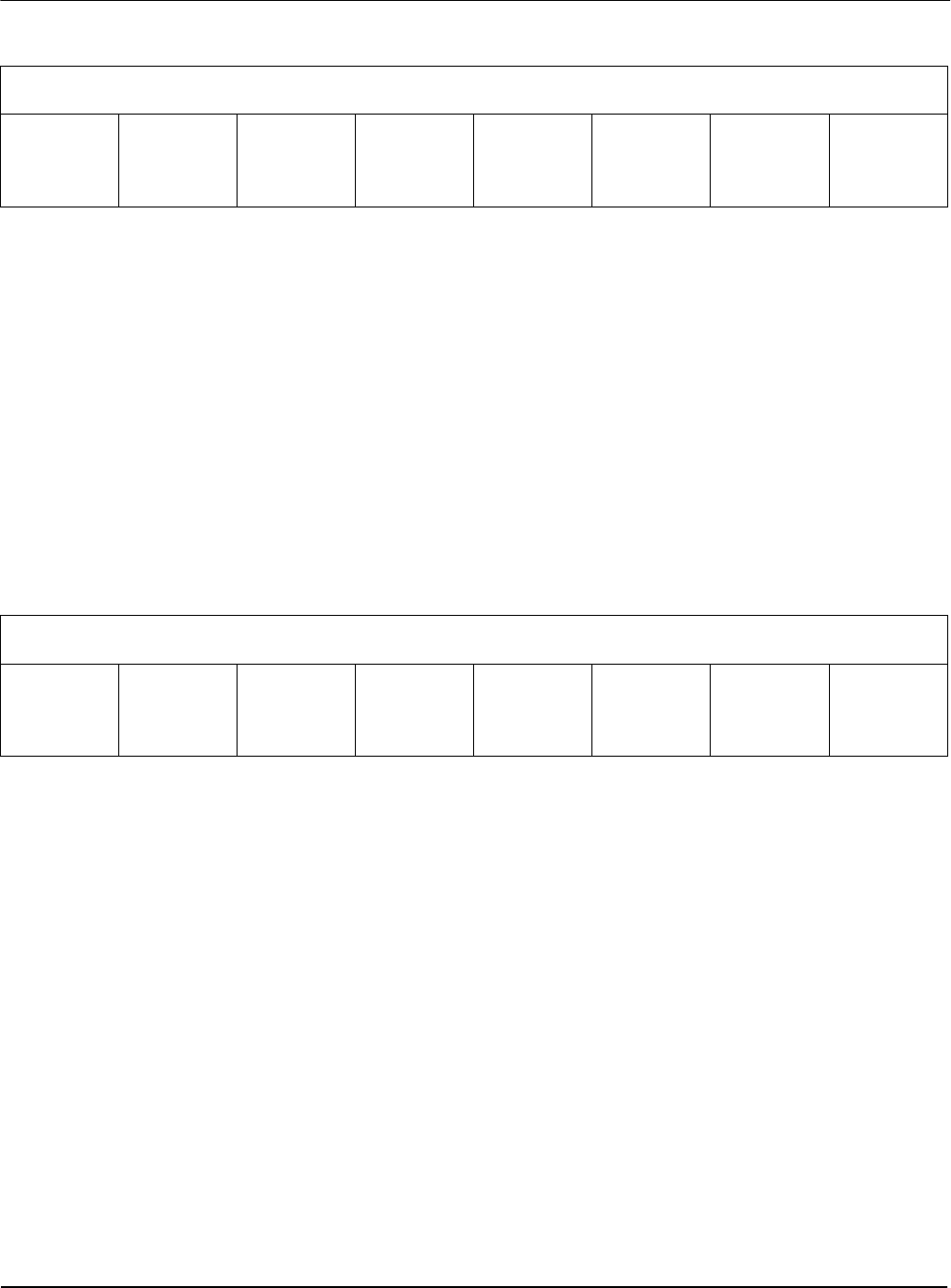

Vertical Non-Display Period Register

REG[0Ah] RW

Vertical

Non-Display

Period Status

(RO)

n/a

Vertical

Non-Display

Period Bit 5

Vertical

Non-Display

Period Bit 4

Vertical

Non-Display

Period Bit 3

Vertical

Non-Display

Period Bit 2

Vertical

Non-Display

Period Bit 1

Vertical

Non-Display

Period Bit 0

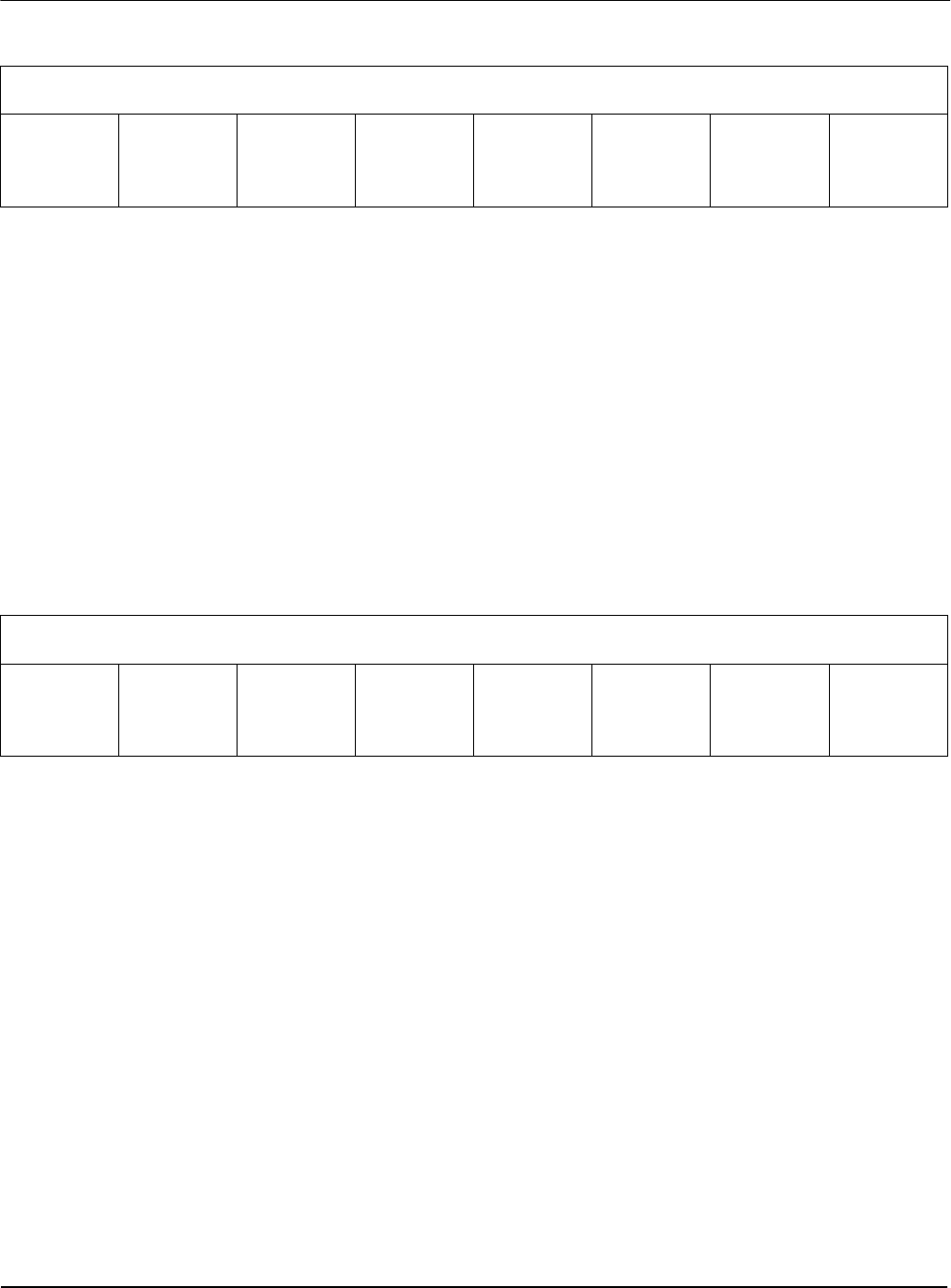

VRTC/FPFRAME Start Position Register

REG[0Bh] RW

n/a n/a

VRTC/

FPFRAME

Start Position

Bit 5

VRTC/

FPFRAME

Start Position

Bit 4

VRTC/

FPFRAME

Start Position

Bit 3

VRTC/

FPFRAME

Start Position

Bit 2

VRTC/

FPFRAME

Start Position

Bit 1

VRTC/

FPFRAME

Start Position

Bit 0