138 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

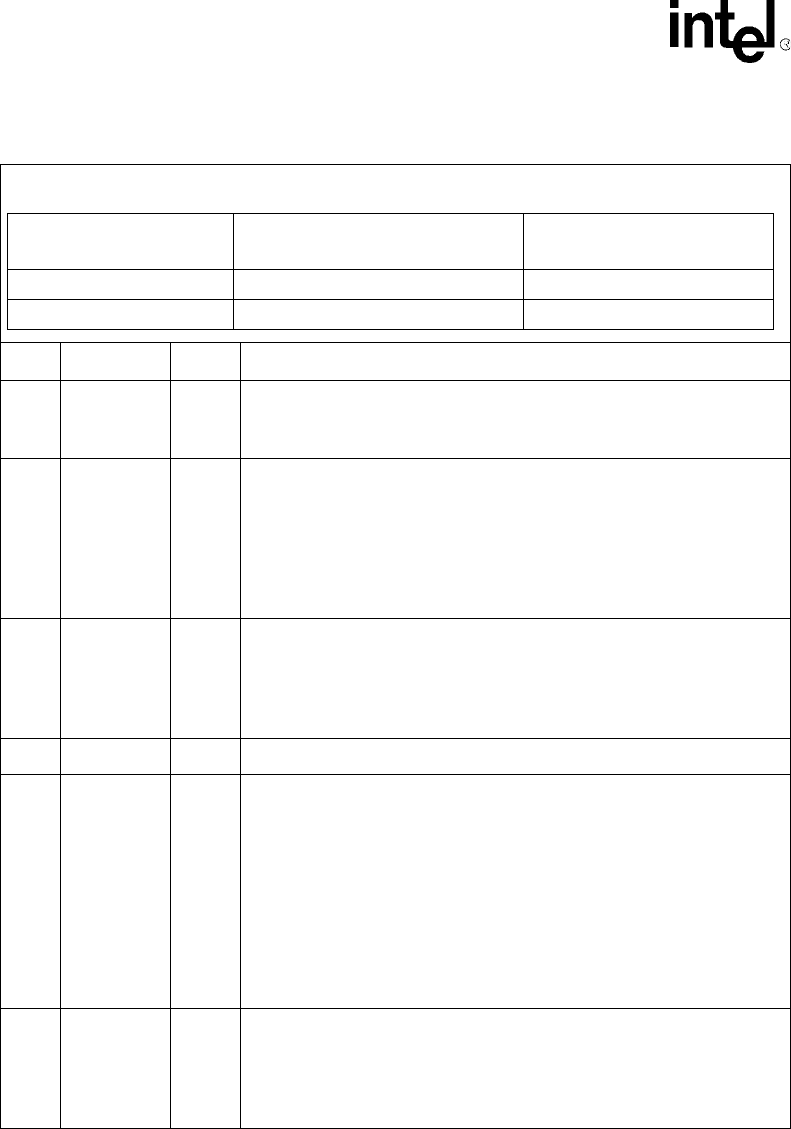

Table 43. Downstream I/O or Memory 1 and Upstream I/O or Memory 0 Setup Registers

These registers may be preloaded by serial ROM or programmed by the local processor before

host configuration.

Bit Name R/W Description

0

Type

Selector

R/(WS)

• When 0, the BAR is requesting memory space, or is disabled.

• When 1, the BAR is requesting I/O space.

• Reset value is 0

2:1 Type R/(WS)

Type of space requested. Allowable values:

• 00b to indicate that the space requested by the BAR may be located

anywhere in memory space, must be used for I/O space

• 01b to indicate that memory space must be mapped below a 1MB

boundary

Other values may have unpredictable results.

Reset value is 00h.

3 Prefetchable R/(WS)

Indicates whether the space requested by the BAR is prefetchable.

• When 0, not prefetchable (required, but not hardware enforced, for I/O

space).

• When 1, prefetchable.

• Reset value is 0

5:4 Reserved R Read only as 0.

30:6 Size R/(WS)

These bits specify the size of the address range requested by the BAR.

• When a bit is 1, the corresponding bit in the BAR functions as a

readable and writable bit.

• When a bit is 0, the corresponding bit in the BAR functions as a

read

-only bit that always returns zero when read.

The PCI Local Bus Specification, Revision 2.2 states that the maximum

value requested for I/O space should not be greater than 256 bytes,

although this is not enforced in hardware. When configured as a memory

range, bits [11:6] should be set to a 0 as the minimum supported memory

range is 4KB.

• Reset value is 0 (disabled).

31 BAR_Enable R/(WS)

BAR enable.

• When 0, the corresponding BAR is disabled and reads as 0.

• When 1, the corresponding BAR is enabled, with size and type

specified by this setup register.

• Reset value is 0

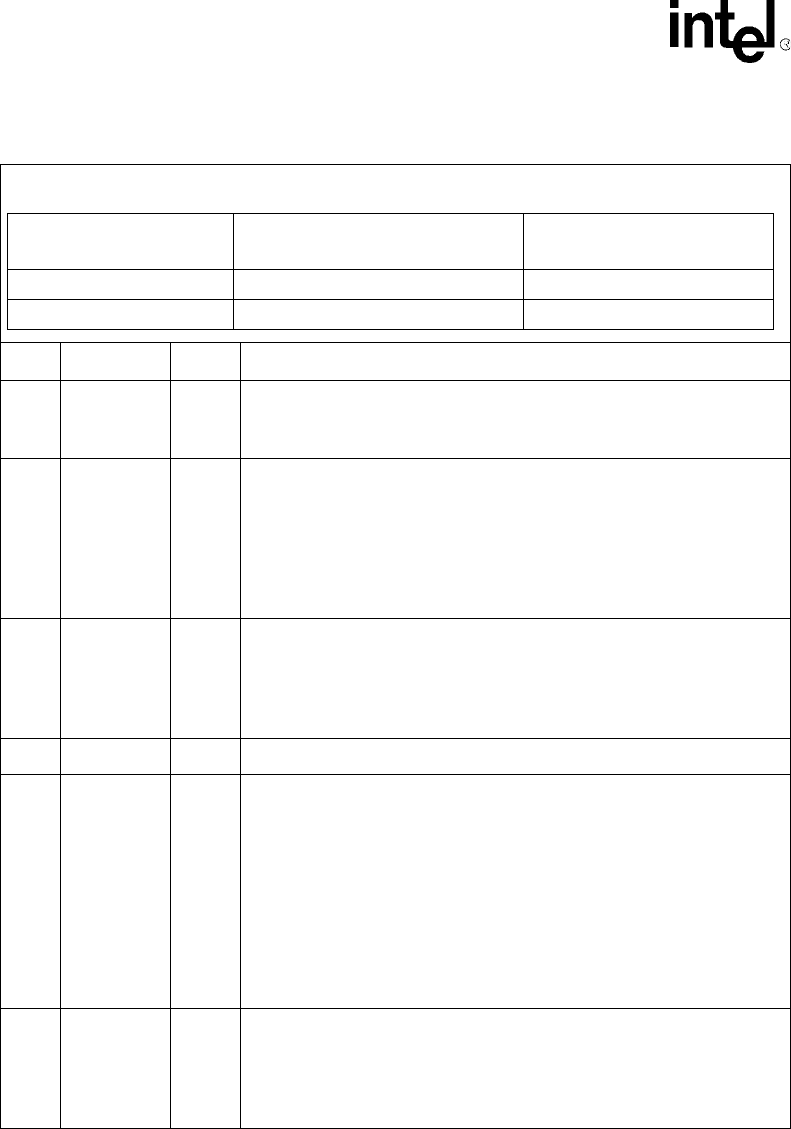

Offsets Downstream I/O or Memory 1 Setup

Upstream I/O or Memory 0

Setup

Primary byte B3:B0h C7:C4h

Secondary byte B3:B0h C7:C4h